Key Takeaways

- Reliable Scaling: Optimized for 12V to 1-5V rails handling 20–45A current density.

- Thermal Efficiency: Ultra-low DCR reduces I²R power loss by up to 50% compared to standard iron-core alternatives.

- Safety Margin: Targeted 20–50% Isat headroom prevents abrupt voltage collapse during transient peaks.

- Footprint Savings: High energy density allows for a 15-20% reduction in PCB real estate compared to legacy high-current inductors.

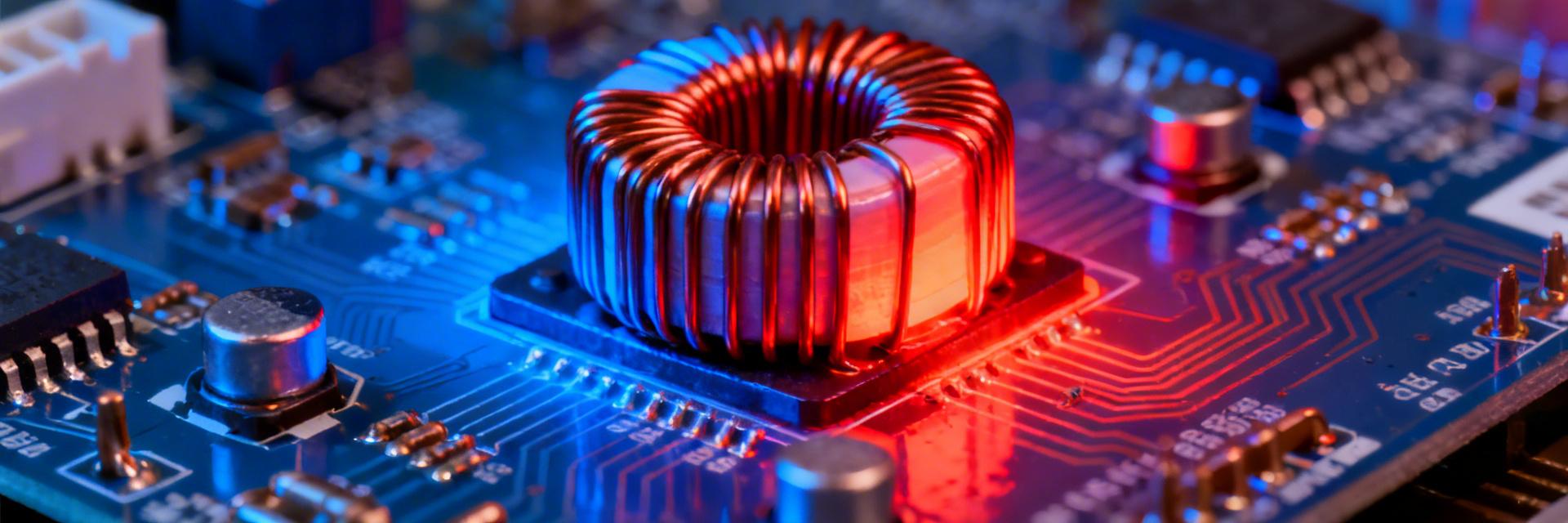

Facing overheating, excessive ripple, or early saturation when designing high-current DC-DC converters? This guide explains how to evaluate and apply the AMELH5030S-R56MT in selecting high-current power inductors for 10–50 A rails so designers achieve reliable, efficient DC-DC design outcomes without time-consuming redesigns. Target rails are 12 V down to low-voltage rails (1–5 V) with typical currents of 20–45 A; the primary outcome is a repeatable margin-based part selection process.

Differential Comparison: AMELH5030S-R56MT vs. Standard Inductors

| Feature | AMELH5030S-R56MT | General High-Current Part | User Benefit |

|---|---|---|---|

| Saturation Curve | Soft Saturation (Stable) | Hard Saturation (Abrupt) | Prevents sudden system reboot on peak load |

| DC Resistance (DCR) | Optimized Minimized | Standard | Extends battery life & reduces heat sinks |

| Thermal Stability | Rated up to 125°C+ | Variable (85-105°C) | Reliable operation in dense enclosures |

| EMI Shielding | Integrated magnetic shield | Often unshielded | Easier FCC/CE certification |

1 — Background: Why the inductor choice matters in high-current DC-DC

1.1 — Role of the power inductor in buck/boost converters

Point: The power inductor transfers energy, shapes ripple, suppresses EMI, and carries thermal loading. Evidence: Inductance, DCR and saturation current determine stored energy and conduction loss. Explanation: Low inductance raises ripple; high DCR increases I²R loss and temperature. Wrong choices show symptoms: excessive output ripple, converter instability, overheating, or abrupt output collapse when Isat is exceeded under transient peaks.

1.2 — Key supplier-agnostic specs to watch (quick checklist)

Point: Watch inductance, DC resistance (DCR), saturation current (Isat), RMS current (Irms), self-resonant frequency (SRF), and thermal impedance. Evidence: For 10–50 A class rails, practical targets are: inductance 100 nH–1 µH, DCR <5–30 mΩ, Isat > peak current by 20–50%, Irms ≥ continuous current, SRF above switching frequency, and low thermal rise. Explanation: These ballpark numbers help narrow choices before detailed simulation or bench tests.

2 — AMELH5030S-R56MT: datasheet-driven spec breakdown

2.1 — Essential electrical specs: inductance, Isat, Irms, DCR, SRF

Point: Read datasheet test conditions—units, tolerance, and bias points matter. Evidence: Isat is usually specified at a % drop in inductance; Irms is thermal-limited. Explanation: Use Isat for peak transient headroom and Irms for continuous heating. Example calculation: for a buck 12 V→1.2 V at 40 A, choose ΔI = 20% of 40 A = 8 A; at Fs = 600 kHz, L = (Vout*(1−D)) / (Fs*ΔI) ≈ (1.2*(1−0.1))/(600e3*8) ≈ 22 nH — but practical designs pick higher L to reduce peak ripple and stress.

2.2 — Thermal and mechanical specs that affect mounting and reliability

Point: Package height, thermal path, rated temperature, and footprint drive reliability. Evidence: DCR plus PCB copper define steady-state temperature rise. Explanation: Ensure pad thermal vias, wide plane copper (oz thickness), and solder fillet integrity. Verify soldering profiles and that the component’s rated Tmax exceeds expected board temperatures; plan for mechanical anchoring if vibration or insertion forces are present.

Engineer's Masterclass: Pro Tips

By: Marcus V. (Senior Power Systems Architect)

"When deploying the AMELH5030S-R56MT, the biggest mistake I see is inadequate copper pour. At 40A, even 1mΩ of trace resistance generates 1.6W of extra heat. Always use at least 2oz copper and treat the inductor as a primary heat-dissipating element."

Typical Layout Strategy

Hand-drawn sketch, not an exact schematic

Troubleshooting Checklist

- Buzzing Noise? Check for saturation under peak load.

- Thermal Shutdown? Increase thermal via density under pads.

- High EMI? Shorten the switch-node loop distance.

3 — How to size inductance and current rating

3.1 — Calculating inductance for target ripple and transient response

Point: Follow a step-by-step calculation: set Fs, pick ΔI, compute L, then validate with converter duty cycle. Evidence: For example 12 V→1.2 V at 40 A, Fs = 600 kHz, D ≈ Vout/Vin = 0.1, ΔI target 8 A yields L ≈ 22–47 nH depending on choice. Explanation: Smaller L reduces transient response time but increases ripple and RMS heating; larger L reduces ripple but can slow transient recovery and require physically larger inductors.

3.2 — Matching saturation and thermal margins

Point: Apply margin rules: Isat should exceed expected peak currents by 20–50%; Irms should exceed continuous current with thermal derating. Evidence: Core bias reduces inductance; temperature increases DCR and lowers Isat. Explanation: Use conservative margins for fault conditions, account for DC bias curves on datasheet, and choose a part whose L vs I curve stays acceptable under expected worst-case temperatures and combined board heating.

4 — Comparing AMELH5030S-R56MT with alternatives

4.1 — DCR and efficiency impact at high current

Point: DCR dominates conduction loss at high current. Evidence: At 30 A, a 10 mΩ DCR causes P = I²R = 9 W loss; reducing DCR to 5 mΩ halves that loss. Explanation: Lower DCR improves efficiency and reduces required cooling, but often increases size, cost, or lowers SRF. Prioritize DCR when efficiency and thermal budget are tight; accept slightly higher DC bias loss if transient response needs are primary.

4.2 — Saturation behavior and thermal runaway risks

Point: Understand hard vs soft saturation and L vs I curves. Evidence: Hard saturation causes abrupt inductance collapse; soft saturation gives gradual loss of inductance. Explanation: Read L(I) curves on datasheet, perform ramp tests, and thermally image the inductor under load. Validate continuous rating with board copper and ambient to avoid thermal runaway in sustained high-current conditions.

5 — Practical layout and testing for 20–45 A rails

5.1 — PCB layout and thermal management best practices

Point: Minimize switch-node loop area, provide wide input/output copper, and use thermal vias under the inductor region. Evidence: Short, wide traces reduce EMI and I²R losses; thermal vias move heat to internal planes. Explanation: Place the inductor close to the switch node, avoid routing under sensitive analog sections, and anchor the component mechanically if needed to withstand reflow and thermal cycling.

5.2 — Bench tests & validation checklist

Point: Essential tests: DC-bias L sweep, thermal imaging at rated load, in-circuit ripple, efficiency curve, surge/fault stress. Evidence: Acceptance thresholds: ΔL under bias <30% at continuous current, temperature rise <40°C above ambient at rated load, ripple within spec for regulator. Explanation: Document failures, replicate root-cause tests, and iterate footprint or heatsinking until criteria are met.

6 — Integration checklist and final recommendations

6.1 — Pre-production checklist

Point: Verify datasheet curves, order evaluation samples, finalize footprint, and run prototype tests. Evidence: Cross-check L(I), DCR, SRF, and thermal curves against measured samples. Explanation: Build a small prototype lot, run life and thermal cycling tests, and include supplier alternates on the BOM to mitigate availability risk before volume production.

6.2 — Risk mitigation and fallback options

Point: When margins are tight, derate, parallel inductors, or choose larger packages. Evidence: Paralleling reduces DCR and shares thermal load; larger parts provide higher Isat and thermal mass. Explanation: Maintain an alternate parts list, define derating policies (e.g., Isat > 1.2×peak), and document substitution rules so field issues trigger controlled part changes rather than ad-hoc fixes.

Summary

Verify required inductance and ripple targets, confirm Isat/Irms and DCR meet margin rules, validate thermal and PCB strategy, and run the bench tests listed — then finalize the AMELH5030S-R56MT selection or its replacement. Careful verification of high-current power inductors early in DC-DC design prevents late-stage redesigns and field failures.

Core Insight Bullet Points

- Match inductance to ripple: compute L from ΔI target and Fs, balancing ripple and transient response.

- Prioritize Isat and Irms margins: choose parts with Isat > peak by ~20–50% and Irms ≥ continuous current.

- Optimize thermal layout: wide copper and thermal vias are essential for high-current longevity.

Common questions and answers

How does AMELH5030S-R56MT perform under DC bias in high-current applications?

The AMELH5030S-R56MT exhibits DC-bias dependent inductance reduction; designers should read L vs I curves and ensure ΔL at operating Irms stays within acceptable limits. Measure a sample under expected bias and temperature to verify in-circuit behavior and avoid unexpected ripple increases or control-loop instability.

What thermal margins should I use for AMELH5030S-R56MT in 30–40 A rails?

Use a rule of thumb: ensure Irms rating exceeds continuous load and allow ≤40°C temperature rise above ambient at rated current. Include board copper thermal modeling, thermal vias, and validate with thermal imaging under worst-case duty to confirm no hot spots.

When should I parallel inductors versus selecting a single AMELH5030S-R56MT?

Parallel inductors when DCR or thermal limits of a single part are exceeded but footprint or height constraints prevent a larger single inductor. Paralleling lowers effective DCR and shares thermal load, but be mindful of current sharing and layout symmetry.